欢迎参与评论,每一条合规评论都是对我们的褒奖。

请 登录 或 快速注册 后发表评论

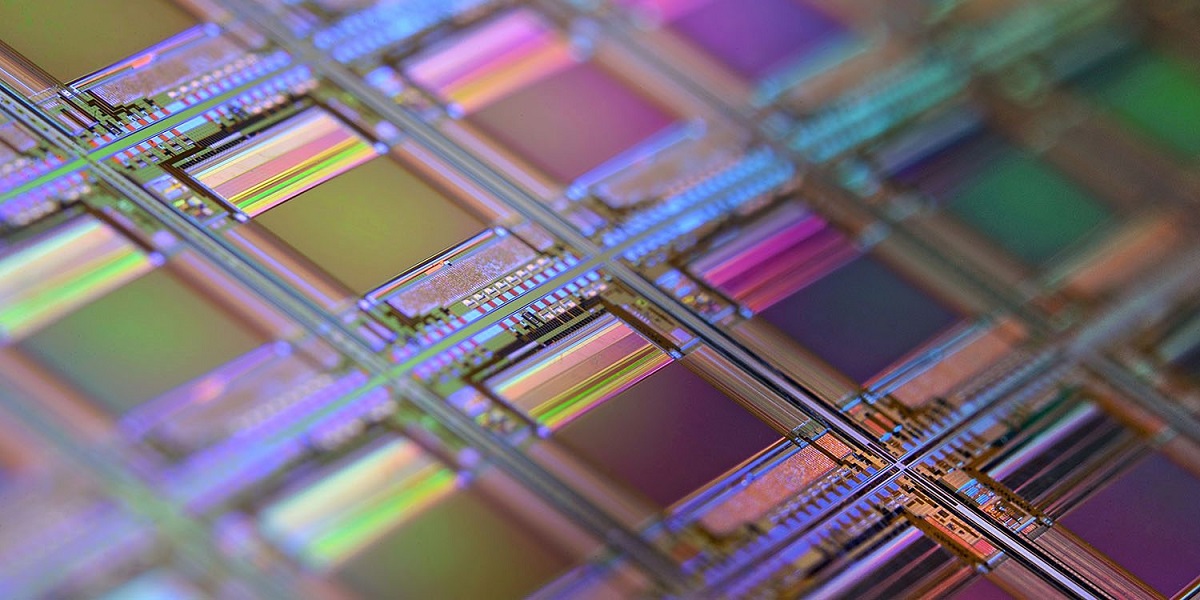

随着半导体工艺进入埃米时代,架构和电路设计也将发生重大调整。为了在正面释放出更多的布局空间,提升逻辑密度和效能,将供电传输转移到背面已成为业界共识,背面供电技术将成为先进半导体制造领域的首选解决方案。目前台积电(TSMC)、三星和英特尔等业界领先厂商都提出了不同的方法,将重点放在晶圆薄化和原子层沉积(ALD)等方面。

据TrendForce报道,台积电所采用的超级电轨(Super Power Rail)架构被认为是最直接有效的解决方案,不过实施起来复杂且成本较高,预计2026年量产。台积电称,超级电轨架构适用于具有复杂讯号及密集供电网络的高性能计算(HPC)产品,将大规模应用于A16制程工艺上,相比于N2P工艺,在相同工作电压下速度快了8-10%,或者在相同速度下,功耗降低了15-20%,同时密度提升了1.1倍。

有业内人士指出,背面供电有几项技术突破,其中一个关键是将背面抛光到足够接近晶体管接触的厚度,但这个过程会大大降低晶圆的刚性。为此正面抛光后,必须粘合载体晶圆以支持背面制造工艺。另外纳米硅通孔(nTSV)等技术需要更多的设备,以确保纳米级孔内的铜金属均匀沉积。随着台积电量产超级电轨架构,相关供应链将会受益。