搭载AMD锐龙AI 300系处理器的笔记本已经在前两天开卖,新的Strix Point处理器的各种信息也开始浮出水面,这款处理器=采用更先进的台积电N4P工艺,但核心尺寸要比上代大的多,它的长宽分别是12.06*18.71mm,而Phoenix和Hawk Point则是9.06*15.01mm,更大的尺寸自然是为了容纳规模更大的CPU、GPU和NPU。

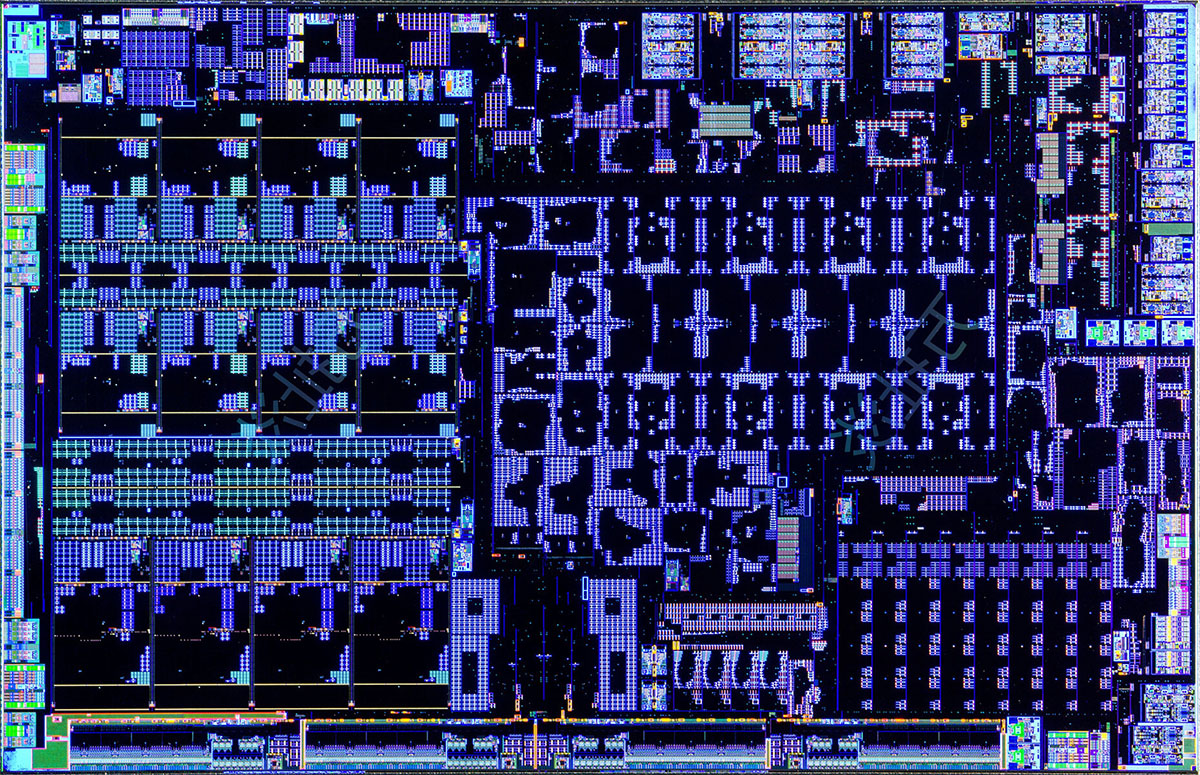

这是由B站Up主万扯淡拍摄的Strix

Point核心照片

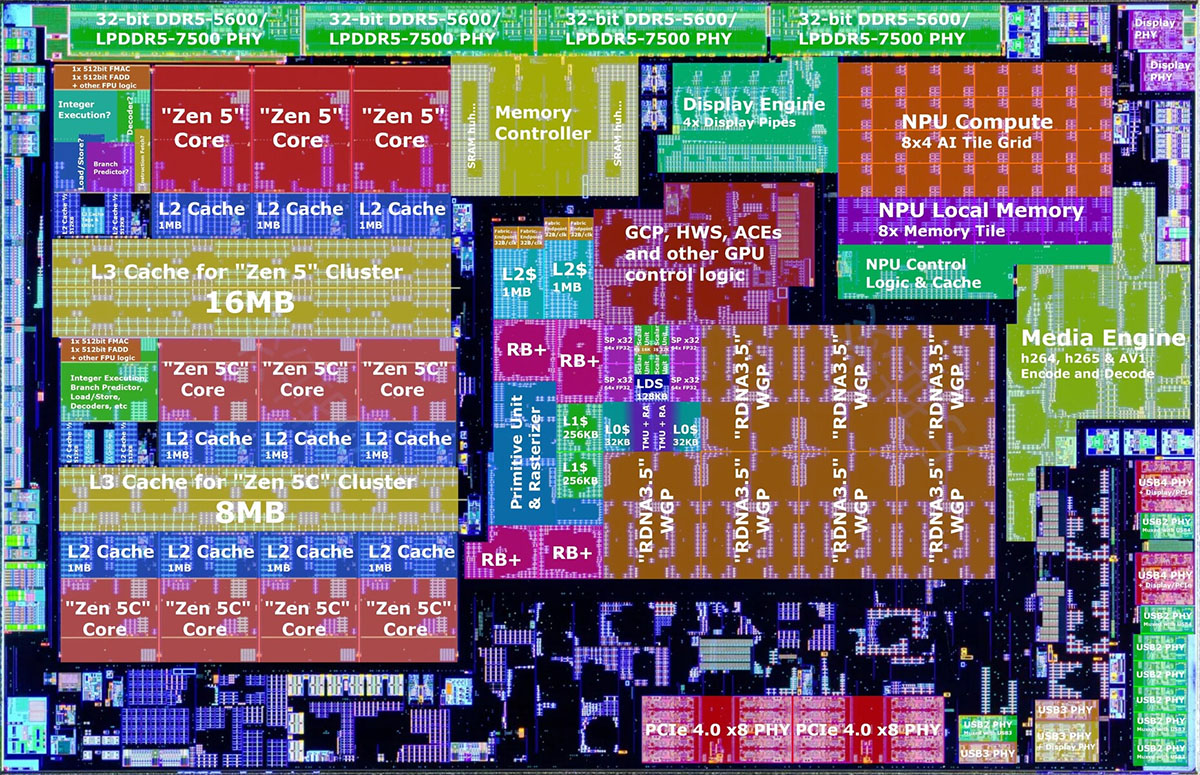

Strix Point的12个CPU分布在两个CCX上,其中一个包含4个Zen 5内核,拥有16MB L3缓存;另一个则拥有8个Zen 5c内核,拥有8MB L3缓存,看起来Zen 5c并没有比Zen 5小很多,两个CCX使用IF总线连接CPU其他部位。

巨大的核显位于CPU芯片的中央,它基于RDNA 3.5架构,包含8组WGP,共16组CU,包含1024个流处理器,拥有4个渲染后端,相当于16个ROP,有不少逻辑控制电路,还有2MB L2缓存。GPU右侧和上方分别是媒体和显示引擎,支持H.264、H.265和AV1等多种视频格式的编解码。显示引擎负责将核显的帧输出编码为各种视频接口格式,最多支持4路视频输出,视频输出的物理层位于CPU边缘。

这是由@GPUsAreMagic所做的注释版本

Strix Point的NPU要比上代大得多,采用新一代XDNA 2架构,拥有32个AI引擎,此外NPU也拥有自己的缓存,根据AMD提供的数据,新的NPU算力达到50 TOPS,已经超过了微软对Copilot+的硬件要求。

四个32bit的内存控制器位于CPU一侧边缘,支持DDR5-5600和LPDDR5-7500内存,内存控制器拥有SRAM缓存,但不清楚具体容量是多少,这仲缓存设计也存在于Phoenix和Phoenix 2芯片上,但桌面处理器的IOD上是没有的。

在过去三代移动处理器上,AMD一直在削减PCIe通道数量,在Cezanne上有24条PCIe通道,到了Phoenix就剩20条,而Strix Point就只剩16条了,当中还要分4条PCIe给USB4,所以实际可分配的只有12条。

我匿名了 07-30 20:29

已有1次举报支持(0) | 反对(1) | 举报 | 回复

9#

旅途终极杀人王 07-30 19:34 | 加入黑名单

已有3次举报支持(0) | 反对(0) | 举报 | 回复

8#

旅途终极杀人王 07-30 17:40 | 加入黑名单

和正常人逻辑存在很大距离的群体:AMD良心,舍的给A卡用最先进的工艺……老黄贪婪为了利润,都是用比AMD低一级的工艺………30系用的三星定制工艺比台积电好~~~~那6000系7000系怎么不用三星定制工艺?

已有4次举报支持(1) | 反对(1) | 举报 | 回复

7#

旅途终极杀人王 07-30 17:28 | 加入黑名单

已有4次举报支持(1) | 反对(1) | 举报 | 回复

6#

我匿名了 07-30 14:03

三星7nm:95.3MTr/mm

台积电7nmFF+:96.5MTr/mm

Intel 10nm:100.76MTr/mm

台积电5nm:171.3MTr/mm

支持(3) | 反对(0) | 举报 | 回复

5#

塔奇克马教授 07-30 13:10 | 加入黑名单

NPU 到底能不能参与FSR

已有1次举报支持(0) | 反对(0) | 举报 | 回复

4#

raidenhuo大学生 07-30 11:44 | 加入黑名单

图一,图二是相反了,我反复对比了一下

支持(0) | 反对(0) | 举报 | 回复

3#

我匿名了 07-30 10:29

采用更先进的台积电N4P工艺……之前有人说AMD都是用比对手差的工艺

已有1次举报支持(1) | 反对(0) | 举报 | 回复

2#

asight等待验证会员 07-30 10:24 | 加入黑名单

辣鸡大小核,这个大小核互访缓存延迟高达180ns+,要知道典型的内存延迟也才50ns~90ns,这大小核算是创纪录了,给个参照物吧:双路EPYC跨socket延迟是280ns。

支持(6) | 反对(0) | 举报 | 回复

1#

提示:本页有 9 个评论因未通过审核而被隐藏