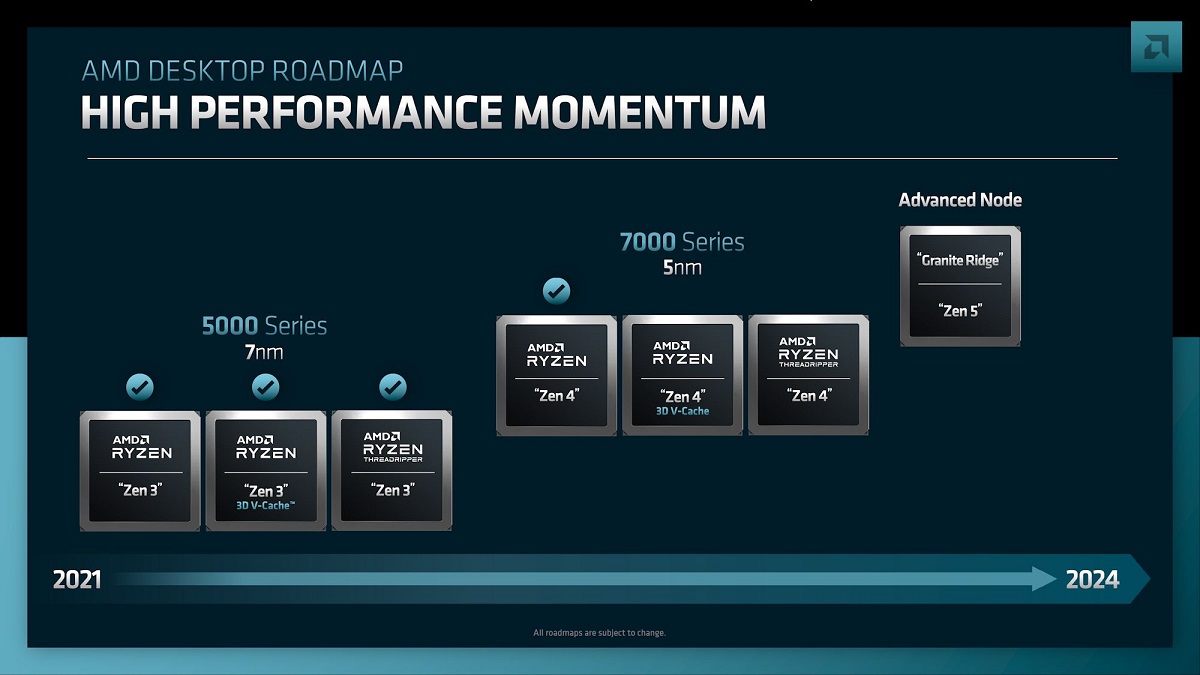

AMD在去年6月的财务分析师日活动上,就已公布了新的CPU产品线路图。显示Zen 4架构将包含Zen 4、Zen 4 V-Cache和Zen 4c三种核心,分别有5nm和4nm版本,到2024年,AMD计划推出全新的Zen 5架构,同样有Zen 5、Zen 5 V-Cache和Zen 5c三个版本,将有4nm和3nm版本。

据RGT报道,Zen 5架构与Zen 4架构相比,IPC可能会有22%到30%的提升。AMD在Zen 5架构上,每个CCX仍然是8个核心,由于Infinity Fabric没有改进,因此“缺乏额外的核心”。传闻旗舰级的Ryzen 9 8000系列最多拥有32个Zen 5架构内核,这意味着要由4个CCX组成。

AMD还会改进Ryzen 8000系列处理器的缓存结构,增大L1缓存,L2缓存可能“在一个CCX上得到统一”。L3缓存可能会被所有核心共享,也可能维持现有的设计,如果是后者,那么AMD或许会加入一个共享的MCD作为L4缓存,不过这只会用于APU。

有消息指出,AMD有意在Zen 5架构上引入混合架构的设计,与英特尔类似。其实去年就有传言,同样属于Ryzen 8000系列的APU会采用混合架构,以Zen 5架构大核搭配Zen 4c架构小核,GPU部分则采用了RDNA 3+架构。

asight等待验证会员 2023-02-09 16:22 | 加入黑名单

intel的单ring架构8+16已经是极限了,没有潜力可挖了,不解决单ring瓶颈就没有未来,8+16在多核规模上走进死胡同了,毕竟ccx架构128核随便做没有极限,而且amd这边随着工艺的进步芯片面积缩小,消费级塞入4个ccx那天就是刷分之战结束的时候。intel要赶紧想办法解决单ring堆多核困难的难题,别在小核电子垃圾上浪费资源了。

已有10次举报支持(35) | 反对(11) | 举报 | 回复

4#

终结之谷瀑布教授 2023-02-09 16:06 | 加入黑名单

我只希望这个IPC的提升,不是通过大小核得来的,而是仅仅大核的架构改进得来的。

已有6次举报小核效率高谁都知道,问题就是多核本身就是一种低效的方式,并行必定会损失性能,也就是跑分里才能真的叠加性能,单核性能仍然是最重要的。

支持(38) | 反对(3) | 举报 | 回复

2#

razorzzh博士 2023-02-11 09:28 | 加入黑名单

您根本没有仔细阅读在下的论点论据,i9-13900K的环状总线链接了8P+16E+Xe核显,实际上它的环状总线已经超过12核了。它的通信延迟体现在WINDOWS 10系统上,由于WIN 10不支持大小核架构,导致12代和13代都只能运行在P-CORE ONLY或者E-CORE ONLY模式上,但是无论何种模式下,通信信号都要走环状总线。现在而言i9-13900K是WIN 10适配度最低的i9。

您根本没有仔细阅读在下的论点论据,i9-13900K的环状总线链接了8P+16E+Xe核显,实际上它的环状总线已经超过12核了。它的通信延迟体现在WINDOWS 10系统上,由于WIN 10不支持大小核架构,导致12代和13代都只能运行在P-CORE ONLY或者E-CORE ONLY模式上,但是无论何种模式下,通信信号都要走环状总线。现在而言i9-13900K是WIN 10适配度最低的i9。

支持(5) | 反对(1) | 举报 | 回复

14#

razorzzh博士 2023-02-11 09:19 | 加入黑名单

10NM 节点

英特尔 1.06亿每平方毫米

台积电 0.53亿每平方毫米

三星 0.52亿每平方毫米

请问英特尔和超威半导体两家中谁的晶体管密度低?

热知识五:

晶体管密度更低的DIE超频优势更大,这是得到IBM FAB IP授权的SAMSUMG FOUNDRY一贯的说辞。按照这个说辞,基于三星授权的应用了格罗方德GF 14NM制程工艺的ZEN系列超频优势应该比应用了INTEL 14NM 的各种SKYLAKE都要大,那请问现实是什么样的?

热知识六:

按照您的理论,MCM多芯片封装技术的制程工艺应该是由其中落后制程工艺定义的。那么在下的光魔G35上的5950X,刃7000P上的5800X,魔霸5R PLUS上的5900HX,这三的IOD都是落后制程,按照您的理论,这三的制程工艺都是应该定义为格罗方德的GF 12NM制程技术了,那么超威半导体发布ZEN 3时的PPT上写明ZEN 3应用的是台积电的TSMC N7P制程工艺在您眼中是虚假宣传了?

10NM 节点

英特尔 1.06亿每平方毫米

台积电 0.53亿每平方毫米

三星 0.52亿每平方毫米

请问英特尔和超威半导体两家中谁的晶体管密度低?

热知识五:

晶体管密度更低的DIE超频优势更大,这是得到IBM FAB IP授权的SAMSUMG FOUNDRY一贯的说辞。按照这个说辞,基于三星授权的应用了格罗方德GF 14NM制程工艺的ZEN系列超频优势应该比应用了INTEL 14NM 的各种SKYLAKE都要大,那请问现实是什么样的?

热知识六:

按照您的理论,MCM多芯片封装技术的制程工艺应该是由其中落后制程工艺定义的。那么在下的光魔G35上的5950X,刃7000P上的5800X,魔霸5R PLUS上的5900HX,这三的IOD都是落后制程,按照您的理论,这三的制程工艺都是应该定义为格罗方德的GF 12NM制程技术了,那么超威半导体发布ZEN 3时的PPT上写明ZEN 3应用的是台积电的TSMC N7P制程工艺在您眼中是虚假宣传了?

支持(0) | 反对(2) | 举报 | 回复

13#

我匿名了 2023-02-10 23:23

已有6次举报支持(0) | 反对(5) | 举报 | 回复

12#

razorzzh博士 2023-02-10 09:04 | 加入黑名单

已有1次举报7NM 节点

英特尔 1.8亿每平方毫米

台积电 0.97亿每平方毫米

三星 0.95亿每平方毫米

5NM 节点

英特尔 3亿每平方毫米

台积电 1.73亿每平方毫米

三星 1.27亿每平方毫米

3NM 节点

英特尔 5.2亿每平方毫米

台积电 2.9亿每平方毫米

三星 1.7亿每平方毫米

现在超威半导体对于英特尔还是有整整一代的领先优势。一旦英特尔达到了5NM节点,考虑到现在的美帝环境和台积电在3NM节点的难产,那么超威半导体的制程优势很有可能不复存在了。

支持(8) | 反对(1) | 举报 | 回复

11#

razorzzh博士 2023-02-10 08:58 | 加入黑名单

已有2次举报热知识二:超威半导体也没有解决环状总线不能超12核的问题,而是通过环状总线和无限总线相结合的方式绕过了这个问题。

热知识三:超威半导体和台积电共同研发的多芯片封装方案MCM实际上是有多核总数限制的,它的多核总数被IOD的运算能力所限制。反而是英特尔的EMIB是没有总数限制的,EMIB方案中每个CPU DIE都可以分配出N个核心当调度核心用,这也是英特尔一直在推大小核方案的原因之一。

支持(10) | 反对(1) | 举报 | 回复

10#

hahaemm博士 2023-02-09 23:38 | 加入黑名单

已有3次举报支持(14) | 反对(2) | 举报 | 回复

9#

我匿名了 2023-02-09 23:22

已有4次举报支持(10) | 反对(2) | 举报 | 回复

8#

lyahehehehe教授 2023-02-09 21:29 | 加入黑名单

已有2次举报支持(12) | 反对(3) | 举报 | 回复

7#

zhaoyun980终极杀人王 2023-02-09 17:06 | 加入黑名单

平台更新不要这么快就好,这B650和DDR5都还没多少人用呢

已有4次举报支持(12) | 反对(5) | 举报 | 回复

6#

龙之海洋研究生 2023-02-09 16:18 | 加入黑名单

经典AMD PPT

已有17次举报从7000系列桌面、7000系列显卡和7000移动端核显的经验来看

这个数字在8000即将发布的时候会打个对折,然后实际提升能有这数字三分之一就不错了

支持(10) | 反对(12) | 举报 | 回复

3#

flare教授 2023-02-09 15:16 | 加入黑名单

本评论因举报过多被折叠 [+]1#

提示:本页有 13 个评论因未通过审核而被隐藏